# SPARC M7<sup>TM</sup> Supplement

to the Oracle SPARC Architecture 2015

Draft D1.0, 30 Jun 2016

Privilege Levels: Privileged

and Nonprivileged

Distribution: Public

Part No: 950-\_\_\_\_-00 Revision: Draft D1.0, 30 Jun 2016  $Copyright @ 2011, Oracle \ and / or \ its \ affiliates. \ All \ rights \ reserved.$

Oracle and Java are registered trademarks of Oracle and/or its affiliates. Other names may be trademarks of their respective owners.

AMD, Opteron, the AMD logo, and the AMD Opteron logo are trademarks or registered trademarks of Advanced Micro Devices. Intel and Intel Xeon are trademarks or registered trademarks of Intel Corporation. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. UNIX is a registered trademark licensed through X/Open Company, Ltd.

# Contents

| 1 | SPA  | ARC M7 Basics 9                                                                                      |

|---|------|------------------------------------------------------------------------------------------------------|

|   | 1.1  | Background 9                                                                                         |

|   | 1.2  | SPARC M7 Overview                                                                                    |

|   | 1.3  | SPARC M7 Components                                                                                  |

|   |      | 1.3.1 SPARC Physical Core                                                                            |

|   |      | 1.3.1.1 Single-threaded and multi-threaded performance 12                                            |

|   |      | 1.3.2 L3 Cache                                                                                       |

| 2 | Data | Formats                                                                                              |

| 3 | Regi | isters                                                                                               |

|   | 3.1  | Floating-Point State Register (FSR)                                                                  |

|   | 3.2  | Ancillary State Registers (ASRs)                                                                     |

|   |      | 3.2.1 Tick Register (TICK)                                                                           |

|   |      | 3.2.2 Program Counter (PC)                                                                           |

|   |      | 3.2.3 Floating-Point Registers State Register (FPRS)                                                 |

|   |      | 3.2.4 General Status Register (GSR)                                                                  |

|   |      | 3.2.5 Software Interrupt Register (SOFTINT)                                                          |

|   |      | 3.2.6 System Tick Register (STICK)                                                                   |

|   |      | 3.2.7 System Tick Compare Register (STICK_CMPR)                                                      |

|   |      | 3.2.8       Compatibility Feature Register (CFR)       21         3.2.9       Pause (PAUSE)       23 |

|   |      | 3.2.10 MWAIT                                                                                         |

|   | 3.3  | Privileged PR State Registers                                                                        |

|   | 0.0  | 3.3.1 Trap State Register (TSTATE)                                                                   |

|   |      | 3.3.2 Processor State Register (PSTATE)                                                              |

|   |      | 3.3.3 Trap Level Register (TL)                                                                       |

|   |      | 3.3.4 Current Window Pointer (CWP) Register                                                          |

|   |      | 3.3.5 Global Level Register (GL)                                                                     |

| 4 | Inst | ruction Format                                                                                       |

| 5 | Inst | ruction Definitions                                                                                  |

|   | 5.1  | Instruction Set Summary                                                                              |

|   | 5.2  | PREFETCH/PREFETCHA35                                                                                 |

|   | 5.3  | WRPAUSE                                                                                              |

|   | 5.4  | WRMWAIT                                                                                              |

|   | 5.5  | Block Load and Store Instructions                                                                    |

|   | 5.6  | Block Initializing Store ASIs                                                                        |

| 6 | Trap | s                                                                                                    |

|   | 6.1  | Trap Levels                                                                                          |

|   | 6.2  | Trap Behavior                                                                                        |

|   | 6.3  | Trap Masking                                                                                         |

| 7  | Inter | rupt Hand        | ling                                                                                                            | . 47             |

|----|-------|------------------|-----------------------------------------------------------------------------------------------------------------|------------------|

|    | 7.1   | Interrupt 1      | Flow                                                                                                            | . 47             |

|    |       | 7.1.1            | Sources                                                                                                         | 47               |

|    |       | 7.1.2            | States                                                                                                          |                  |

|    | 7.2   | CPU Inter        | rupt Registers                                                                                                  | . 47             |

|    |       | 7.2.1            | Interrupt Queue Registers                                                                                       |                  |

| _  |       |                  |                                                                                                                 |                  |

| 8  | Mem   | •                | s                                                                                                               |                  |

|    | 8.1   | Supported        | Memory Models                                                                                                   |                  |

|    |       | 8.1.1            | TSO                                                                                                             |                  |

|    |       | 8.1.2            | RMO                                                                                                             | 52               |

| 9  | Addı  | ress Spaces      | and ASIs                                                                                                        | . 53             |

|    | 9.1   | -                | paces                                                                                                           |                  |

|    | 7.1   | 9.1.1            | 54-bit Virtual and Real Address Spaces                                                                          |                  |

|    | 0.2   |                  | <del>-</del>                                                                                                    |                  |

|    | 9.2   | 9.2.1            | Address Spaces                                                                                                  |                  |

|    |       | 9.2.1            | ASI_REAL_ASI_REAL_LITTLE, ASI_REAL_IO, and ASI_REAL                                                             | _10_LITTLE (ASIS |

|    |       | 9.2.2            | 1416, 1C16, 1516, 1D16) 60<br>ASI_SCRATCHPAD (ASI 2016, VA 016-1816, 3016-3816)                                 | 60               |

|    |       |                  |                                                                                                                 |                  |

| 10 | Perfo | ormance In       | strumentation                                                                                                   | . 61             |

|    | 10.1  | Introducti       | on                                                                                                              | . 61             |

|    | 10.2  | SPARC Pe         | rformance Control Registers                                                                                     | . 61             |

|    | 10.3  | SPARC Pe         | rformance Instrumentation Counter                                                                               | . 62             |

| 11 | т 1   |                  | D 1 '                                                                                                           | <b></b>          |

| 11 | _     |                  | n Dependencies                                                                                                  |                  |

|    | 11.1  |                  | General Information                                                                                             |                  |

|    |       | 11.1.1           | Level-2 Compliance (Impdep #1)                                                                                  |                  |

|    |       | 11.1.2           | Unimplemented Opcodes, ASIs, and ILLTRAP                                                                        |                  |

|    |       | 11.1.3           | Trap Levels (Impdep #37, 38, 39, 40, 114, 115)                                                                  |                  |

|    |       | 11.1.4           | Trap Handling (Impdep #16, 32, 33, 35, 36, 44)                                                                  |                  |

|    |       | 11.1.5           | Secure Software                                                                                                 |                  |

|    | 44.0  | 11.1.6           | Address Masking (Impdep #125)                                                                                   |                  |

|    | 11.2  |                  | perations                                                                                                       |                  |

|    |       | 11.2.1           | Integer Register File and Window Control Registers (Impdep #2)                                                  |                  |

|    |       | 11.2.2           | Clean Window Handling (Impdep #102)                                                                             |                  |

|    |       | 11.2.3<br>11.2.4 | Integer Multiply and Divide                                                                                     |                  |

|    | 11 0  |                  | MULScc                                                                                                          |                  |

|    | 11.3  |                  | P Floating-Point Operations                                                                                     |                  |

|    |       | 11.3.1<br>11.3.2 | Overflow, Underflow, and Inexact Traps (Impdep #3, 55)                                                          |                  |

|    |       | 11.3.2           | Quad-Precision Floating-Point Operations (Impdep #3) Floating-Point Upper and Lower Dirty Bits in FPRS Register |                  |

|    |       | 11.3.4           | Floating-Point Status Register (FSR) (Impdep #13, 19, 22, 23, 24)                                               |                  |

|    | 11.4  |                  | Memory-Related Operations                                                                                       |                  |

|    | 11.4  | 11.4.1           | Load/Store Alternate Address Space (Impdep #5, 29, 30)                                                          |                  |

|    |       | 11.4.1           | Read/Write ASR (Impdep #6, 7, 8, 9, 47, 48)                                                                     |                  |

|    |       | 11.4.3           | MMU Implementation (Impdep #41)                                                                                 |                  |

|    |       | 11.4.4           | FLUSH and Self-Modifying Code (Impdep #122)                                                                     |                  |

|    |       | 11.4.5           | PREFETCH{A} (Impdep #103, 117)                                                                                  |                  |

|    |       | 11.4.6           | LDD/STD Handling (Impdep #107, 108)                                                                             |                  |

|    |       | 11.4.7           | FP mem_address_not_aligned (Impdep #109, 110, 111, 112)                                                         |                  |

|    |       | 11.4.8           | Supported Memory Models (Impdep #113, 121)                                                                      |                  |

|    |       | 11.4.9           | Implicit ASI When TL > 0 (Impdep #124)                                                                          |                  |

|    | 11.5  |                  | RC V9 Extensions                                                                                                |                  |

|    |       | 11.5.1           | Cache Subsystem                                                                                                 |                  |

|    |       | 11.5.2           | Block Memory Operations                                                                                         |                  |

|    |       | 11.5.3           | Partial Stores                                                                                                  |                  |

|    |       | 11.5.4     | Short Floating-Point Loads and Stores                     | 71  |

|----|-------|------------|-----------------------------------------------------------|-----|

|    |       | 11.5.5     | Load Twin Extended Word                                   |     |

|    |       | 11.5.6     | SPARC M7 Instruction Set Extensions (Impdep #106)         |     |

|    |       | 11.5.7     | Performance Instrumentation                               |     |

|    |       | 11.5.8     | ASI MONITOR AS IF USER PRIMARY, ASI MONITOR               |     |

|    |       | 11.0.0     | ASI_MONITOR_PRIMARY, ASI_MONITOR_SECONDAR                 |     |

|    |       |            |                                                           |     |

| 12 | Cryp  | tographic  | Extensions                                                | 73  |

|    | 12.1  | CFR Regi   | ster                                                      | 73  |

|    |       | _          | aphic Instructions                                        |     |

|    |       |            | aphic performance                                         |     |

|    |       |            | 7 crypto coding guidance                                  |     |

|    |       |            |                                                           |     |

| 13 | Mem   | ory Mana   | gement Unit                                               | 75  |

|    | 13.1  | Translatio | on Table Entry (TTE)                                      | 75  |

|    | 13.2  |            | on Storage Buffer (TSB)                                   |     |

|    | 13.3  |            | lated Faults and Traps                                    |     |

|    | 10.0  | 13.3.1     | IAE_privilege_violation Trap                              |     |

|    |       | 13.3.2     | IAE_nfo_page Trap                                         |     |

|    |       | 13.3.3     | DAE_privilege_violation Trap                              |     |

|    |       | 13.3.4     | DAE_side_effect_page Trap                                 |     |

|    |       | 13.3.5     | DAE_nc_page Trap                                          |     |

|    |       | 13.3.6     | DAE_invalid_asi Trap                                      |     |

|    |       | 13.3.7     | DAE_nfo_page Trap                                         |     |

|    |       | 13.3.8     | privileged_action Trap                                    |     |

|    |       | 13.3.9     | This trap occurs when an access is attempted using a rest |     |

|    |       | 10.0.7     | privileged mode (PSTATE.priv = 0). *mem_address_n         |     |

|    | 13 4  | MMII On    | eration Summary                                           | - * |

|    | 13.5  |            | on                                                        |     |

|    | 13.3  |            |                                                           |     |

|    |       | 13.5.1     | Instruction Translation                                   |     |

|    |       | 12 F 2     | 13.5.1.1 Instruction Prefetching                          |     |

|    | 10.6  | 13.5.2     | Data Translation                                          |     |

|    | 13.6  | -          | ace With the SPARC V9 Annex F                             |     |

|    | 13.7  |            | ernal Registers and ASI Operations                        |     |

|    |       | 13.7.1     | Accessing MMU Registers                                   |     |

|    |       | 13.7.2     | Context Registers                                         | 85  |

| Δ  | Prog  | rammino (  | Guidelines                                                | 151 |

| 11 | _     | _          |                                                           |     |

|    | A.1   |            | eading                                                    |     |

|    |       | A.1.1      | Instruction fetch                                         |     |

|    |       | A.1.2      | Select/Decode/Rename                                      |     |

|    |       | A.1.3      | Pick/Issue/Execute                                        |     |

|    |       | A.1.4      | Commit.                                                   |     |

|    |       | A.1.5      | Context Switching Between Strands                         |     |

|    |       | A.1.6      | Synchronization                                           |     |

|    | A.2   | -          | ing for Single-Threaded Performance or Throughput         |     |

|    | A.3   | Instructi  | on Latency                                                | 153 |

| В  | IEEE  | 754 Floati | ng-Point Support                                          | 163 |

|    |       |            |                                                           |     |

|    | B.1   | Special C  | Operand and Result Handling                               | 103 |

| C  | Diffe | erences Be | tween SPARC M7 and SPARC M6                               | 165 |

|    | C.1   | Architec   | tural and Microarchitectural Differences                  | 166 |

|    | C.2   |            | Spaces and ASIs Differences                               |     |

|    |       | C.2.1      | ASIs                                                      |     |

|    |       |            |                                                           |     |

| D | Cache  | Coheren        | cy and Ordering                               | 167 |

|---|--------|----------------|-----------------------------------------------|-----|

|   | D.1    | Cache an       | nd Memory Interactions                        | 167 |

|   | D.2    | Cache Fl       | ushing                                        | 167 |

|   |        | D.2.1          | Displacement Flushing                         | 168 |

|   |        | D.2.2          | Memory Accesses and Cacheability              | 168 |

|   |        | D.2.3          | Coherence Domains                             | 168 |

|   |        |                | D.2.3.1 Cacheable Accesses                    |     |

|   |        |                | D.2.3.2 Noncacheable and Side-Effect Accesses | 169 |

|   |        |                | D.2.3.3 Global Visibility and Memory Ordering | 169 |

|   |        | D.2.4          | Memory Synchronization: MEMBAR and FLUSH      |     |

|   |        |                | D.2.4.1 MEMBAR #LoadLoad                      |     |

|   |        |                | D.2.4.2 MEMBAR #StoreLoad                     |     |

|   |        |                | D.2.4.3 MEMBAR #LoadStore                     |     |

|   |        |                | D.2.4.4 MEMBAR #StoreStore and STBAR          |     |

|   |        |                | D.2.4.5 MEMBAR #Lookaside                     |     |

|   |        |                | D.2.4.6 MEMBAR #MemIssue                      |     |

|   |        |                | D.2.4.7 MEMBAR #Sync (Issue Barrier)          |     |

|   |        | D 0 5          | D.2.4.8 Self-Modifying Code (FLUSH)           |     |

|   |        | D.2.5          | Atomic Operations                             |     |

|   |        |                | D.2.5.1 SWAP Instruction                      |     |

|   |        |                | D.2.5.2 LDSTUB Instruction                    |     |

|   |        | D 2 (          | D.2.5.3 Compare and Swap (CASX) Instruction   | 172 |

|   | D 2    | D.2.6          | Nonfaulting Load                              |     |

|   | D.3    |                | he                                            |     |

|   |        | D.3.1          | LRU Replacement Algorithm                     |     |

|   |        | D.3.2          | Direct-Mapped Mode                            |     |

|   | D 4    | D.3.3          | I-Cache Disable                               |     |

|   | D.4    |                | che                                           |     |

|   |        | D.4.1          | LRU Replacement Algorithm                     |     |

|   |        | D.4.2          | Direct-Mapped Mode                            |     |

|   | D. =   | D.4.3          | D-Cache Disable                               |     |

|   | D.5    |                | action Cache                                  |     |

|   |        | D.5.1          | NRU Replacement Algorithm                     |     |

|   |        | DFO            | D.5.1.1 Mapping Out Lines                     |     |

|   |        | D.5.2          | Directory Coherence                           |     |

|   | D.     | D.5.3          | L2I Cache Disable                             |     |

|   | D.6    |                | Cache                                         |     |

|   |        | D.6.1          | NRU Replacement Algorithm                     |     |

|   |        | D.6.2          | D.6.1.1 Mapping Out Lines                     |     |

|   |        | D.6.2<br>D.6.3 | L2 Cache Disable                              |     |

|   |        |                |                                               |     |

| E | Gloss  | ary            |                                               | 179 |

| F | Biblio | graphy         |                                               | 181 |

|   |        |                |                                               |     |

|   | Index  |                |                                               | 183 |

### SPARC M7 Basics

## 1.1 Background

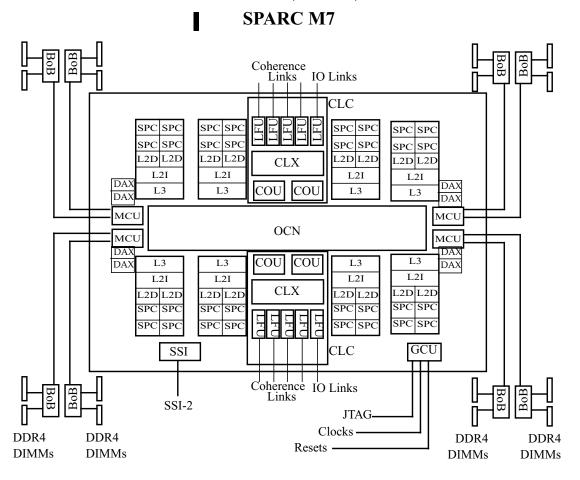

SPARC M7 is the follow-on chip multi-threaded (CMT) processor to the SPARC M6 processor. SPARC M7 incorporates a new processor core (Core S4) a new L2 cache, and a new L3 cache structure. IO has moved off chip to an external ASIC, connected to SPARC M7 with a high speed serial link interface.

The SPARC M7 product line fully implements Oracle's Throughput Computing initiative for the horizontal system space. Throughput Computing is a technique that takes advantage of the thread-level parallelism that is present in most commercial workloads. Unlike desktop workloads, which often have a small number of threads concurrently running, most commercial workloads achieve their scalability by employing large pools of concurrent threads.

SPARC M7 supports up to a eight way glueless (without external hub chips) coherent system using 7 coherence link channels. SPARC M7 has 32 SPARC physical processor cores. Each core has full hardware support for eight strands, two integer execution pipelines, one floating-point execution pipeline, and one memory pipeline. The SPARC cores are connected to L2 and L3 caches. There are 8 L3 caches, each is 8 MB, 2-banked, 8 way associative per bank.

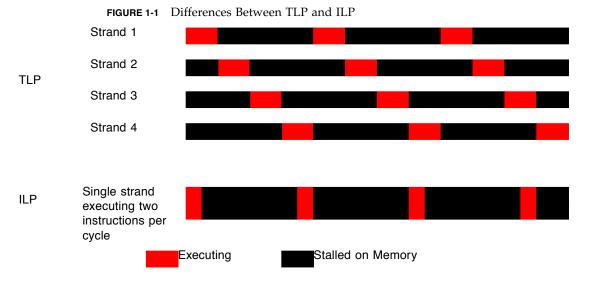

Historically, microprocessors have been designed to target desktop workloads, and as a result have focused on running a single thread as quickly as possible. Single thread performance is achieved in these processors by a combination of extremely deep pipelines (over 20 stages in Pentium 4) and by executing multiple instructions in parallel (referred to as instruction-level parallelism or ILP). The basic tenet behind Throughput Computing is that exploiting ILP and deep pipelining has reached the point of diminishing returns, and as a result current microprocessors do not utilize their underlying hardware very efficiently. For many commercial workloads, the processor is idle most of the time waiting on memory, and even when it is executing it will often be able to only utilize a small fraction of its wide execution width. So rather than building a large and complex ILP processor that sits idle most of the time, a number of small, single-issue processors that employ multithreading are built in the same chip area. Combining multiple processors on a single chip with multiple strands per

processor provides very high performance for highly threaded commercial applications. This approach is called thread-level parallelism (TLP), and the difference between TLP and ILP is shown in the FIGURE 1-1.

The memory stall time of one strand can often be overlapped with execution of other strands on the same processor, and multiple processors run their strands in parallel. In the ideal case, shown in FIGURE 1-1, memory latency can be completely overlapped with execution of other strands. In contrast, instruction-level parallelism simply shortens the time to execute instructions and does not help much in overlapping execution with memory latency.<sup>1</sup>

Given this ability to overlap execution with memory latency, why don't more processors utilize TLP? The answer is that designing processors is a mostly evolutionary process, and the ubiquitous deeply pipelined, wide ILP processors of today are the evolutionary outgrowth from a time when the processor was the bottleneck in delivering good performance. With processors capable of multiple GHz clocking, the performance bottleneck has shifted to the memory and I/O subsystems, and TLP has an obvious advantage over ILP for tolerating the large I/O and memory latency prevalent in commercial applications.

Unlike first-generation TLP processors, SPARC M7 seeks to provide the best of TLP and ILP processors. In particular, SPARC M7 provides a robust out-of-order, dual-issue processor core that is heavily threaded among eight strands. It has a 16-stage integer pipeline to achieve high operating frequencies, advanced branch prediction to mitigate the effect of a deep pipeline, and dynamic allocation of processor resources to threads. This allows SPARC M7 to achieve very high single-thread performance while still scaling to very high levels of throughput.

## 1.2 SPARC M7 Overview

SPARC M7 is a chip multi-threaded (CMT) processor which supports cache-coherent multi-socket systems. SPARC M7 contains 32 SPARC physical processor cores. Two SPARC physical cores connect to a single 256 KB L2 data cache of 2 banks and 8 ways, and four SPARC physical cores connect to a single 256 KB L2 instruction cache of 2 banks and 8 ways. The L2 instruction and data caches connect

<sup>1.</sup> Processors that employ out-of-order ILP can overlap some memory latency with execution. However, this overlap is typically limited to shorter memory latency events such as L1 cache misses that hit in the L2 cache. Longer memory latency events such as main memory accesses are rarely overlapped to a significant degree with execution by an out-of-order processor.

to an L3 cache. L2 and L3 caches have 64-byte lines. Each L3 cache is banked two ways and is local to the four SPARC cores, the two L2 data caches, and the L2 instruction cache that attach to each L3 cache. This collection of four cores, L2 caches, and L3 cache is called a SPARC Cache Cluster (SCC).

# 1.3 SPARC M7 Components

This section describes each component in SPARC M7.

### 1.3.1 SPARC Physical Core

Each SPARC physical core has hardware support for eight strands. This support consists of a full integer register file with eight register windows per strand, a full floating-point register file per strand, and nearly all of the ASI, ASR, and privileged registers replicated per strand. The eight strands share the instruction and data caches. Each SPARC physical core has a 16 KB, 4-way set-associative instruction cache with 64-byte lines, a 16 KB, 4-way set-associative data cache (32-byte lines) that are shared by the eight strands. The L1 data cache is write-through and does not allocate on a write miss; the L2 is store-in and allocates on a write miss. All strands share a floating-point unit incorporating fused multiply-add and VIS3.0 instruction support.

Two physical cores share a 256KB, 8-way set-associative L2D cache with 64B lines. Four physical cores share a 256KB, 8-way set-associative L2I cache with 64B lines.

· 11

The strands share a dual-issue, out-of-order pipeline, divided into two "slots". One instruction can be issued each cycle to each slot. Slot 0 contains an integer unit and a load/store unit, while slot 1 contains an integer unit, a branch unit, and a floating-point and graphics unit. Up to two instructions can complete each cycle for a peak operation rate of two instructions per cycle. The pipeline is both horizontally and vertically threaded; various segments of the pipeline handle strands differently. The instruction fetch unit fetches instructions from a given strand each cycle. Strands are selected for fetching based upon a least-recently-fetched algorithm. Once fetched, strands are then selected for decoding in a least-recently-decoded fashion and are then renamed and supplied into an out-of-order processor core. Once inside the out-of-order core, strands are picked for issue independently between slots, and in an oldest-ready-first fashion within a slot. Instructions complete out-of-order and are committed in-order within a strand, but independently between strands. Up to 128 instructions can be in flight within the processor core, in any combination across the active strands. In certain circumstances, hardware may activate heuristics to avoid starvation or performance imbalances resulting from unfair access to hardware resources. The L1 cache load-use latency is 5 cycles, the L2 cache load-use latency is 19 cycles, and the L3 load-use latency is 41 cycles.

### 1.3.1.1 Single-threaded and multi-threaded performance

SPARC M7 is dynamically threaded. While software can activate up to 8 strands on each core at a time, hardware dynamically and seamlessly allocates core resources such as instruction, data, and L2 caches, and out-of-order execution resources such as the 128-entry re-order buffer in the core, among the active strands.

Since the core dynamically allocates resources among the active strands, there is no explicit "single-thread mode" or "multi-thread mode" for software to activate or deactivate. The extent to which strands compete for core resources depends upon their execution characteristics. These characteristics include cache footprints, inter-instruction dependencies in their execution streams, branch prediction effectiveness, and others. Consider one process which has a small cache footprint and a high correct branch prediction rate which, when running alone on a core, achieves 2 instructions per cycle (SPARC M7's peak rate of instruction execution). We term this a high-IPC process. If another process with similar characteristics is activated on a different strand on the same core, each of the strands will likely operate at approximately 1 instruction per cycle. In other words, the single-thread performance of each process has been cut in half. As a rule of thumb, activating N high-IPC strands will result in each strand executing at 1/N of its peak rate, assuming each strand is capable of executing close to 2 instructions per cycle.

Now consider a process which is largely memory-bound. Its native IPC will be small, perhaps 0.2. If this process runs on one strand on a core with another clone process running on a different strand, there is a good chance that both strands will suffer no noticeable performance loss, and the core throughput will improve to 0.4 IPC. If a low-IPC process runs on one strand with a high-IPC process running on another strand, it's likely that the IPC of either strand will not be greatly perturbed. The high-IPC strand may suffer a slight performance degradation (as long as the low-IPC strand does not cause a substantial increase in cache miss rates for the high-IPC strand).

The guidelines above are only general rules-of-thumb. The extent to which one strand affects another strand's performance depends upon many factors. Processes which run fine on their own but suffer from destructive cache interference when run with other strands may suffer unacceptable performance losses. Similarly, it is also possible for strands to cooperatively improve performance when run together. This may occur when the strands running on one core share code or data. In this case, one strand may prefetch instructions or data that other strands will use in the near future.

The same discussion can apply between cores running in the chip. Since the L3 cache and memory controllers are shared between the cores, activity on one core can influence the performance of strands on another core.

### 1.3.2 L3 Cache

Each of the eight L3 cache is banked two ways. It is inclusive of all chip-local L2 caches. Each L3 cache is 8 Mbytes, and each bank is 8-way set associative. The line size is 64 bytes.

## CHAPTER 2

# Data Formats

Data formats supported by SPARC M7 are described in the Oracle SPARC Architecture 2015 specification.

## Registers

# 3.1 Floating-Point State Register (FSR)

Each virtual processor has a Floating-Point State register. This register follows the Oracle SPARC Architecture 2015 specification, with the ver and qne fields permanently set to 0 (SPARC M7 does not support a FQ).

For more information on this register, see the Oracle SPARC Architecture 2015 specification.

# 3.2 Ancillary State Registers (ASRs)

This chapter discusses the SPARC M7 ancillary state registers. TABLE 3-1 summarizes and defines these registers.

■ TABLE 3-1 Summary of SPARC M7 Ancillary State Registers

| ASR<br>number | ASR Name        | Access | priv  | Description                                         |

|---------------|-----------------|--------|-------|-----------------------------------------------------|

| 0             | Υ               | RW     | N     | Y Register                                          |

| 1             | Reserved        | _      |       | Any access causes a <i>illegal_instruction</i> trap |

| 2             | CCR             | RW     | N     | Condition Code register                             |

| 3             | ASI             | RW     | N     | ASI register                                        |

| 4             | TICK            | RO     | $Y^1$ | TICK register                                       |

| 5             | PC              | $RO^2$ | N     | Program counter                                     |

| 6             | FPRS            | RW     | N     | Floating-Point Registers Status register            |

| 07 - 13       | Reserved        | -      |       | Any access causes an illegal_instruction trap       |

| 15            | (MEMBAR, STBAR) | _      | N     | Instruction opcodes only, not an actual ASR.        |

| 16 - 18       | Reserved        | _      |       | Any access causes an illegal_instruction trap       |

| 19            | GSR             | RW     | N     | General Status register                             |

| 20            | SOFTINT_SET     | W      | $Y^4$ | Set bit in Soft Interrupt register                  |

| 21            | SOFTINT_CLR     | W      | $Y^4$ | Clear bit in Soft Interrupt register                |

TABLE 3-1 Summary of SPARC M7 Ancillary State Registers (Continued)

| ASR<br>number | ASR Name   | Access | priv           | Description                                                             |

|---------------|------------|--------|----------------|-------------------------------------------------------------------------|

| 22            | SOFTINT    | RW     | Y <sup>3</sup> | Soft Interrupt register                                                 |

| 23            | Reserved   | -      |                | Any access causes an illegal_instruction trap                           |

| 24            | STICK      | RW     | $Y^5$          | System Tick register                                                    |

| 25            | STICK_CMPR | RW     | $Y^3$          | System TICK Compare register                                            |

| 26            | CFR        | $RO^6$ | Y              | Compatibility Feature Register                                          |

| 27            | PAUSE      | W      | N              | Any read causes an <i>illegal_instruction</i> trap; PAUSE is write-only |

| 28            | MWAIT      | W      | N              | Any read causes an <i>illegal_instruction</i> trap; MWAIT is write-only |

| 29 - 31       | Reserved   | _      |                | Any access causes an <i>illegal_instruction</i> trap                    |

#### Notes:

- 1. An attempted write by nonprivileged software to this register causes a *privileged\_opcode* trap.An attempted write by privileged software to this register causes an *illegal\_instruction* trap. See the Oracle SPARC Architecture 2015 specification for more detail.

- 2. A write to this register causes an illegal\_instruction trap.

- 3. An attempted access in nonprivileged mode causes a *privileged\_opcode* trap.

- 4. Read accesses cause an *illegal\_instruction* trap. An attempted write access in nonprivileged mode causes a *privileged\_opcode* trap.

- 5. A write by privileged or user software causes an *illegal\_instruction* trap. See the Oracle SPARC Architecture 2015 specification for more detail.

- 6. Reads are nonprivileged. A write by privileged or user software causes an *illegal\_instruction* trap.

## 3.2.1 Tick Register (TICK)

The TICK register contains one field: counter. The counter field is shared by the eight strands on a physical core. The counter increments each processor core clock. The format of this register is shown in TABLE 3-2.

For more information on this register, see the Oracle SPARC Architecture 2015 specification.

**TABLE 3-2** TICK Register – TICK (ASR 04<sub>16</sub>)

| Bit  | Field   | RW | Description                                               |

|------|---------|----|-----------------------------------------------------------|

| 63   | _       | RO | Reserved                                                  |

| 62:0 | counter | RW | Tick counter, increments each processor core clock cycle. |

## 3.2.2 Program Counter (PC)

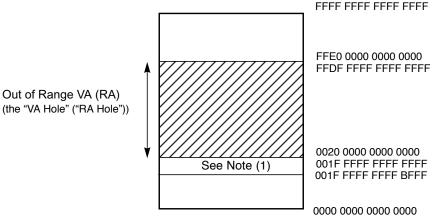

Each strand has a read-only program counter register. The PC contains a 54-bit virtual address and VA{63:54} is sign-extended from VA{53}. The format of this register is shown in TABLE 3-3.

**TABLE 3-3** Program Counter – PC (ASR  $05_{16}$ )

| Bit   | Field   | R/W | Description                                               |

|-------|---------|-----|-----------------------------------------------------------|

| 63:54 | va_high | RO  | Sign-extended from VA{53}.                                |

| 53:2  | va      | RO  | Virtual address contained in the program counter.         |

| 1:0   | _       | RO  | The lower 2 bits of the program counter always read as 0. |

## 3.2.3 Floating-Point Registers State Register (FPRS)

This register is described in Oracle SPARC Architecture 2015.

Note SPARC M7 sets FPRS.du or FPRS.dl when an instruction that updates the floating-point register file successfully completes, or when an FMOVcc or FMOVr instruction that does not satisfy the destination register update condition successfully completes.

## 3.2.4 General Status Register (GSR)

Each virtual processor has a nonprivileged general status register (GSR). When PSTATE.pef or FPRS.fef is zero, accesses to this register cause an *fp\_disabled* trap.

For more information on this register, see the Oracle SPARC Architecture 2015 specification.

## 3.2.5 Software Interrupt Register (SOFTINT)

Each virtual processor has a privileged software interrupt register. Nonprivileged accesses to this register cause a *privileged\_opcode* trap. The SOFTINT register contains two fields: sm, and int\_level. Note that while setting the sm (bit 16) or SOFTINT{14} bits generate *interrupt\_level\_14*, these bits are considered completely independent of each other. Thus an STICK compare will only set bit 16 and generate *interrupt\_level\_14*, not also set bit 14.

TABLE 3-4 specifies how interrupt\_level\_14 is shared between SOFTINT writes and STICK compares.

TABLE 3-4 Sharing of interrupt\_level\_14

| Event                                                | SOFTINT{14} | sm        | Action                                                         |

|------------------------------------------------------|-------------|-----------|----------------------------------------------------------------|

| STICK compare when $sm = 0$                          | Unchanged   | 1         | interrupt_level_14 if<br>PSTATE.ie = 1 and PIL < 14            |

| Set $sm = 1$ when $sm = 0$                           | Unchanged   | 1         | <pre>interrupt_level_14 if PSTATE.ie = 1 and PIL &lt; 14</pre> |

| Set SOFTINT $\{14\} = 1$ when SOFTINT $\{14\} = 0$ . | 1           | Unchanged | <pre>interrupt_level_14 if PSTATE.ie = 1 and PIL &lt; 14</pre> |

For more information on this register, see the Oracle SPARC Architecture 2015 specification.

## 3.2.6 System Tick Register (STICK)

Each SPARC M7 physical processor core implements an STICK register, shared by all strands of that core.

#### TABLE 3-5 System Tick Register – STICK (ASR 18<sub>16</sub>)

| Bit  | Field | R/W | Description                                         |

|------|-------|-----|-----------------------------------------------------|

| 63   | _     | RO  | Reserved.                                           |

| 62:0 | stick | RW  | Elapsed time value, measured in increments of 1 nS. |

Privileged software can read the STICK register with the RDSTICK instruction. Privileged software cannot write the STICK register; an attempt by privileged software to execute the WRSTICK instruction results in an *illegal\_instruction* exception.

Nonprivileged software can read the STICK register with RDSTICK instruction. Nonprivileged software cannot write the STICK register; an attempt by nonprivileged software to execute the WRSTICK instruction results in an *illegal\_instruction* exception.

In SPARC M7, the difference of the values of two different reads of the STICK register reflects the amount of time that has passed between the reads;

(value2 - value1) \* 1 = the number of nanoseconds that passed between the reads.

For more information on this register, see the Oracle SPARC Architecture 2015 specification.

## 3.2.7 System Tick Compare Register (STICK\_CMPR)

Each virtual processor has a privileged System Tick Compare (STICK\_CMPR) register. Nonprivileged accesses to this register cause a *privileged\_opcode* exception. STICK\_CMPR contains two fields: int\_dis and stick\_cmpr. Only bits 62:9 of the stick\_cmpr field are compared against the STICK counter field.

The int\_dis bit controls whether a STICK interrupt\_level\_14 interrupt is posted in the SOFTINT register when STICK\_CMPR bits 62:9 match STICK bits 62:9. The format of this register is shown in TABLE 3-6.

**TABLE 3-6** System Tick Compare Register – STICK\_CMPR (ASR 19<sub>16</sub>)

| Bit  | Field      | R/W | Description                                                                    |

|------|------------|-----|--------------------------------------------------------------------------------|

| 63   | int_dis    | RW  | stick_int interrupt disable. If 1, stick_int interrupt generation is disabled. |

| 62:9 | stick_cmpr | RW  | Compare value for stick_int interrupts.                                        |

| 8:0  | _          | RO  | Reserved.                                                                      |

After a power-on reset trap, STICK\_CMPR.int\_dis is set to 1 and STICK\_CMPR.cmpr is undefined.

An *stick\_match* exception occurs in the cycle in which all of the following three conditions are met:

- 1.  $STICK\_CMPR.int\_dis == 0$ .

- 2. A transition occurs from

(STICK.counter)[62:9] < STICK\_CMPR.cmpr[62:9]

in one cycle, to

(STICK.counter)[62:9] >= STICK\_CMPR.cmpr[62:9]

in the following cycle

3. This transition of state occurs due to incrementing STICK, and not due to writing STICK, or STICK\_CMPR

When an *stick\_match* interrupt occurs, SOFTINT{16} (sm) is set to 1. This has the effect of posting an *interrupt\_level\_14* trap request to the virtual processor, which causes an *interrupt\_level\_14* trap when (PIL < 14) and (PSTATE.ie == 1). The *interrupt\_level\_14* trap handler must check SOFTINT{14} and SOFTINT{16} (sm) to determine the cause of the *interrupt\_level\_14* trap.

The reason the comparison of STICK\_CMPR and STICK ignore bits 8 to 0 (and the reason STICK\_CMPR is not implemented below bit 9) is because at the minimum frequency of the processor core, the STICK register could reflect as much as 384 ns passing between cycles (due to acceleration of the STICK register increment by the 'drift fix').

For more information on this register, see the Oracle SPARC Architecture 2015 specification.

## 3.2.8 Compatibility Feature Register (CFR)

For general information on this register, see the Oracle SPARC Architecture 2015 specification.

Each virtual processor has a compatibility feature register (CFR). The CFR is read-only. The format of the CFR is shown in Table 3-7.

**TABLE 3-7** Compatibility Feature Register – CFR (ASR 1A<sub>16</sub>)

| Bit   | Field    | R/W | Description                                                                                                                                                                                           |

|-------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63:15 | _        | RO  | Reserved                                                                                                                                                                                              |

| 14    | xmontsqr | RO  | If set, the processor supports the XMONTSQR opcode. If not set, an attempt to execute an XMONTSQR instruction results in a <i>compatibility_feature</i> trap.                                         |

| 13    | xmontmul | RO  | If set, the processor supports the XMONTMUL opcode. If not set, an attempt to execute an XMONTMUL instruction results in a <i>compatibility_feature</i> trap.                                         |

| 12    | xmpmul   | RO  | If set, the processor supports the XMPMUL opcode. If not set, an attempt to execute an XMPMUL instruction results in a <i>compatibility_feature</i> trap.                                             |

| 11    | crc32c   | RO  | If set, the processor supports the CRC32C opcode. If not set, an attempt to execute a CRC32C instruction results in a <i>compatibility_feature</i> trap.                                              |

| 10    | montsqr  | RO  | If set, the processor supports the MONTSQR opcode. If not set, an attempt to execute a MONTSQR instruction results in a <i>compatibility_feature</i> trap.                                            |

| 9     | montmul  | RO  | If set, the processor supports the MONTMUL opcode. If not set, an attempt to execute a MONTMUL instruction results in a <i>compatibility_feature</i> trap.                                            |

| 8     | mpmul    | RO  | If set, the processor supports the MPMUL opcode. If not set, an attempt to execute an MPMUL instruction results in a <i>compatibility_feature</i> trap.                                               |

| 7     | sha512   | RO  | If set, the processor supports the SHA512 opcode. If not set, an attempt to execute a SHA512 instruction results in a <i>compatibility_feature</i> trap.                                              |

| 6     | sha256   | RO  | If set, the processor supports the SHA256 opcode. If not set, an attempt to execute a SHA256 instruction results in a <i>compatibility_feature</i> trap.                                              |

| 5     | sha1     | RO  | If set, the processor supports the SHA1 opcode. If not set, an attempt to execute a SHA1 instruction results in a <i>compatibility_feature</i> trap.                                                  |

| 4     | md5      | RO  | If set, the processor supports the MD5 opcode. If not set, an attempt to execute an MD5 instruction results in a <i>compatibility_feature</i> trap.                                                   |

| 3     | camellia | RO  | If set, the processor supports Camellia opcodes (CAMELLIA_F, CAMELLIA_FL, and CAMELLIA_FLI). If not set, an attempt to execute a Camellia instruction results in a <i>compatibility_feature</i> trap. |

· 21

**TABLE 3-7** Compatibility Feature Register – CFR (ASR 1A<sub>16</sub>)

| Bit | Field | R/W | Description                                                                                                                                                                                                                                                                                                                      |

|-----|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | _     | RO  | Reserved                                                                                                                                                                                                                                                                                                                         |

| 1   | des   | RO  | If set, the processor supports DES opcodes (DES_ROUND, DES_IP, DES_IIP, and DES_KEXPAND). If not set, an attempt to execute a DES instruction results in a <i>compatibility_feature</i> trap.                                                                                                                                    |

| 0   | aes   | RO  | If set, the processor supports AES opcodes (AES_EROUND01, AES_EROUND23, AES_DROUND01, AES_DROUND23, AES_EROUND_01_LAST, AES_EROUND_23_LAST, AES_DROUND_01_LAST, AES_DROUND_23_LAST, AES_KEXPAND0, AES_KEXPAND1, and AES_KEXPAND2). If not set, an attempt to execute an AES instruction results in a compatibility_feature trap. |

The CFR enumerates the capabilities that SPARC M7 supports. While the current definition of the CFR only relates to cryptographic capability, additional capabilities may be added in future processors. Software can use the CFR to determine whether a set of cryptographic opcodes associated with a cryptographic function can be executed on an instance of SPARC M7. Hardware also uses the CFR to determine whether a cryptographic capability associated with an opcode is present. When SPARC M7 executes a cryptographic opcode, it associates a bit in the CFR with each opcode; the bit must be set, otherwise a *compatibility\_feature* trap occurs.

| Programming | For optimal performance, prior to using instruction-level        |

|-------------|------------------------------------------------------------------|

| Note        | cryptographic functions, applications and libraries should first |

|             | check the CFR to ensure that the desired algorithm is supported  |

|             | by the hardware.                                                 |

The CFR allows software to construct an architecture that enables opcode reuse. A complete discussion is outside the scope of this document; however, a brief overview follows.

Consider the situation where a processor is introduced that supports three cryptographic opcodes: opA, opB, and opC. Cryptographic requirements could be such that opA=AES, opB=DES, and opC=Kasumi. Traditionally, for any derivative or next-generation processor for which different ciphers were of interest, it would be necessary to expend additional opcodes to achieve the necessary support: e.g. opD=Camellia, opE=MD5. OpA, OpB, and OpC would still be consumed in these follow-on processors, even if there was no longer any interest in the AES, DES, and Kasumi algorithms.

In conjunction with appropriate software architecture and infrastructure, the CFR enables opcode reuse by future processor generations when cryptographic algorithms become obsolete. Potential aliasing problems are disambiguated using the CFR. Each bit in the CFR is permanently assigned to a different cryptographic operation. For instance, bits 0, 1, and 2 are assigned to AES, DES, and Kasumi family opcodes, as shown above. The mapping in the CFR is fixed for all future and derivative processors. When an application wishes to perform an AES operation, it registers that request using the appropriate software architectural means, and uses opA in its binary. Prior to executing, system software or the application checks to make sure that the target processor binds the AES function to opA. It does so by examining the CFR to see if bit 0 is set. If so, the program executes using native AES instructions (opA); if not, system software and/or the application must support a non-native AES instruction implementation using standard instructions. It is expected that cryptographic libraries will contain the necessary checking, so hardware cryptographic support will be transparent to applications that perform cryptographic operations using cryptographic library calls. If the application does not use cryptographic libraries, it should check the CFR to make sure that hardware supports the appropriate function, otherwise it should emulate the function using standard instructions. Alternatively, if performance is not critical, it may rely on trap-and-emulate support provided by higher-level system software.

When the first generation of processor (G1) executes an AES opcode it checks that CFR bit 0 is set. If so, the hardware performs the requested AES operation. Accordingly, on G1, an application is free to perform AES operations using opA. Similar enforcement is applied to DES and Kasumi, respectively.

Now consider what happens if the application is moved to a future processor (G2) which has re-used opA to provide support for Camellia; i.e. opA=Camellia. When system software checks the capabilities for the program, or the program checks, it will see that G2 does not support AES using opA (CFR bit 0 will be 0). This allows system software or the application to emulate AES support using standard instructions. Note that if the application somehow runs without this check having been performed and issues opA, the G2 processor will examine the CFR bit for Camellia, and if set, the application will execute, and get erroneous results (Camellia instead of AES). A similar problem exists if the application is developed for G2 hardware, but somehow runs on a G1 processor. Thus it is vital that system software and/or the application appropriately register their intent and check hardware capability prior to executing cryptographic opcodes.

As a result, given appropriate software infrastructure, instruction set designers may reuse opcodes to perform a variety of different operations and applications will continue to see the expected results on different generation platforms.

### 3.2.9 Pause (PAUSE)

SPARC M7 physically implements a 16-bit PAUSE register. The value written to the PAUSE register via the WRPAUSE instruction is an unsigned 20-bit value that is then right-shifted by 4 bits (divided by 16) since hardware decrements the PAUSE register once every 16 ns. Thus the unsigned 16-bit value represents a count from 0 to a maximum of 1048576 ns. Writing to the non-privileged PAUSE register stalls a thread for the number of nanoseconds specified by the XOR of the source operands, except as follows:

- 1. Writing 0 to the PAUSE register stalls the thread for the minimum time (greater than zero since there is a minimum stall time due to internal pipeline delays).

- 2. Writing a value larger than  $2^{20}$  1 causes hardware to saturate the 16-bit PAUSE register; hardware sets PAUSE to F\_FFF0<sub>16</sub> prior to decrementing it.

- 3. If the STICK register is disabled (not measuring time), then writing any value to the PAUSE register behaves the same as writing 0 to the PAUSE register.

When the PAUSE register is written to a nonzero value, the strand is scheduled to be flushed and made inactive (i.e., all resources released by that strand, no core activity other than PAUSE register maintenance and monitoring for unmasked disrupting exceptions). No instructions are fetched by the strand while its PAUSE register is nonzero. An unmasked disrupting exception terminates the PAUSE. Once the PAUSE register reaches value 0 or an unmasked disrupting exception occurs, the virtual processor restarts fetch and execution of the strand. The reactivated strand restarts at either the instruction following the WRPAUSE or a disrupting trap handler.

For more information on this instruction, see the Oracle SPARC Architecture 2015 specification or Section 5.3, WRPAUSE, on page 36.

Note | Prior implementations implemented PAUSE based on cycles, not not nanoseconds. Software written for prior implementations using PAUSE may need to adjust due to this change.

### 3.2.10 MWAIT

SPARC M7 shares the physical implementation of the PAUSE register for much of the MWAIT register functionality. That is, the counters for the PAUSE and MWAIT registers are physically the same counter. See the description of the PAUSE register in Section 3.2.9, *Pause (PAUSE)*, on page 23.

For more information on MWAIT, see the Oracle SPARC Architecture 2015 specification.

· 23

# 3.3 Privileged PR State Registers

TABLE 3-8 lists the privileged registers.

**TABLE 3-8** Privileged Registers

| Register | Register Name | Access | Description                    |

|----------|---------------|--------|--------------------------------|

| 0        | TPC           | RW     | Trap PC <sup>1</sup>           |

| 1        | TNPC          | RW     | Trap Next PC <sup>1</sup>      |

| 2        | TSTATE        | RW     | Trap State                     |

| 3        | TT            | RW     | Тгар Туре                      |

| 4        | TICK          | RW     | Tick                           |

| 5        | TBA           | RW     | Trap Base Address <sup>1</sup> |

| 6        | PSTATE        | RW     | Process State                  |

| 7        | TL            | RW     | Trap Level                     |

| 8        | PIL           | RW     | Processor Interrupt Level      |

| 9        | CWP           | RW     | Current Window Pointer         |

| 10       | CANSAVE       | RW     | Savable Windows                |

| 11       | CANRESTORE    | RW     | Restorable Windows             |

| 12       | CLEANWIN      | RW     | Clean Windows                  |

| 13       | OTHERWIN      | RW     | Other Windows                  |

| 14       | WSTATE        | RW     | Window State                   |

| 16       | GL            | RW     | Global Level                   |

<sup>1.</sup> SPARC M7 only implements bits 53:0 of the TPC, TNPC, and TBA registers. Bits 63:54 are always sign-extended from bit 53.

## 3.3.1 Trap State Register (TSTATE)

Each virtual processor has *MAXPTL* (2) Trap State registers. These registers hold the state values from the previous trap level. The format of one element the TSTATE register array (corresponding to one trap level) is shown in TABLE 3-9.

TABLE 3-9 Trap State Register

| Bit   | Field      | R/W | Description                                  |

|-------|------------|-----|----------------------------------------------|

| 63:42 | _          | RO  | Reserved.                                    |

| 41:40 | gl         | RW  | Global level at previous trap level          |

| 39:32 | ccr        | RW  | CCR at previous trap level                   |

| 31:24 | asi        | RW  | ASI at previous trap level                   |

| 23:21 | _          | RO  | Reserved                                     |

| 20    | pstate tct | RW  | PSTATE.tct at previous trap level            |

| 18    | _          | RO  | Reserved (corresponds to bit 10 of PSTATE)   |

| 17    | pstate cle | RW  | PSTATE.cle at previous trap level            |

| 16    | pstate tle | RW  | PSTATE.tle at previous trap level            |

| 15:13 | _          | RO  | Reserved (corresponds to bits 7:5 of PSTATE) |

**TABLE 3-9** Trap State Register (Continued)

| Bit | Field       | R/W | Description                               |

|-----|-------------|-----|-------------------------------------------|

| 12  | pstate pef  | RW  | PSTATE.pef at previous trap level         |

| 11  | pstate am   | RW  | PSTATE.am at previous trap level          |

| 10  | pstate priv | RW  | PSTATE.priv at previous trap level        |

| 9   | pstate ie   | RW  | PSTATE.ie at previous trap level          |

| 8   | _           | RO  | Reserved (corresponds to bit 0 of PSTATE) |

| 7:3 | _           | RO  | Reserved                                  |

| 2:0 | cwp         | RW  | CWP from previous trap level              |

For more information on this register, see the Oracle SPARC Architecture 2015 specification.

## 3.3.2 Processor State Register (PSTATE)

Each virtual processor has a Processor State register. More details on PSTATE can be found in the Oracle SPARC Architecture 2015 specification. The format of this register is shown in TABLE 3-10; note that the memory model selection field (mm) mentioned in Oracle SPARC Architecture 2015 is not implemented in SPARC M7.

**TABLE 3-10** Processor State Register

| Bit   | Field        | R/W | Description                                |

|-------|--------------|-----|--------------------------------------------|

| 63:13 | _            | RO  | Reserved                                   |

| 12    | tct          | RW  | Trap on control transfer                   |

| 10    | <del>_</del> | RO  | Reserved                                   |

| 9     | cle          | RW  | Current little endian                      |

| 8     | tle          | RW  | Trap little endian                         |

| 7:6   | <del>_</del> | RO  | Reserved (mm; not implemented in SPARC M7) |

| 5     | <del>_</del> | RO  | Reserved                                   |

| 4     | pef          | RW  | Enable floating-point                      |

| 3     | am           | RW  | Address mask                               |

| 2     | priv         | RW  | Privileged mode                            |

| 1     | ie           | RW  | Interrupt enable                           |

| 0     | _            | RO  | Reserved (was ag)                          |

**Programming** | Hyperprivileged changes to translation in delay slots of delayed Note | control transfer instructions should be avoided.

For more information on this register, see the Oracle SPARC Architecture 2015 specification.

## 3.3.3 Trap Level Register (TL)

Each virtual processor has a Trap Level register. Writes to this register saturate at MAXPTL (2). This saturation is based on bits 2:0 of the write data; bits 63:3 of the write data are ignored.

For more information on this register, see the Oracle SPARC Architecture 2015 specification.

### 3.3.4 Current Window Pointer (CWP) Register

Since *N\_REG\_WINDOWS* = 8 on SPARC M7, the CWP register in each virtual processor is implemented as a 3-bit register.

25

For more information on this register, see the Oracle SPARC Architecture 2015 specification.

## 3.3.5 Global Level Register (GL)

Each virtual processor has a Global Level register, which controls which set of global register windows is in use. The maximum global level (MAXPGL) for SPARC M7 is 2. GL is implemented as a 2-bit register on SPARC M7. On a trap, GL is set to min(GL + 1,MAXPTL).

Writes to the GL register saturate at MAXPTL. This saturation is based on bits 1:0 of the write data; bits 63:2 of the write data are ignored.

The format of the GL register is shown in TABLE 3-11.

#### TABLE 3-11 Global Level Register

| Bit  | Field | R/W | Description   |

|------|-------|-----|---------------|

| 63:2 | _     | RO  | Reserved      |

| 1:0  | gl    | RW  | Global level. |

For more information on this register, see the Oracle SPARC Architecture 2015 specification.

# **Instruction Format**

Instruction formats are described in the Oracle SPARC Architecture 2015 specification.

## **Instruction Definitions**

# 5.1 Instruction Set Summary

The SPARC M7 CPU implements the Oracle SPARC Architecture 2015 instruction set.

TABLE 5-1 lists the complete SPARC M7 instruction set supported in hardware. All instructions that are part of Oracle SPARC Architecture 2015 are documented in the Oracle SPARC Architecture 2015 specification; any instructions that are extensions to OSA 2011 are documented in this chapter.

■ TABLE 5-1 Complete SPARC M7 Hardware-Supported Instruction Set (1 of 6)

| Opcode Complete Si  | Paccylition                                                  |

|---------------------|--------------------------------------------------------------|

|                     | Description                                                  |

| ADD (ADDcc)         | Add (and modify condition codes)                             |

| ADDC (ADDCcc)       | Add with carry (and modify condition codes)                  |

| ADDXC (ADDXCcc)     | Add extended with carry (and modify condition codes)         |

| AES_DROUND01        | AES decrypt round, columns 0 & 1                             |

| AES_DROUND23        | AES decrypt round, columns 2 & 3                             |

| AES_DROUND01_LAST   | AES decrypt last round, columns 0 & 1                        |

| AES_DROUND23_LAST   | AES decrypto last round, columns 2 & 3                       |

| AES_EROUND01        | AES encrypt round, columns 0 & 1                             |

| AES_EROUND23        | AES encrypt round, columns 2 & 3                             |

| AES_EROUND01_LAST   | AES encrypt last round, columns 0 & 1                        |

| AES_EROUND23_LAST   | AES encrypt last round, columns 2 & 3                        |

| AES_KEXPAND0        | AES key expansion without round constant                     |

| AES_KEXPAND1        | AES key expansion with round constant                        |

| AES_KEXPAND2        | AES key expansion without SBOX                               |

| ALIGNADDRESS        | Calculate address for misaligned data access                 |

| ALIGNADDRESS_LITTLE | Calculate address for misaligned data access (little-endian) |

| ALLCLEAN            | Mark all windows as clean                                    |

| AND (ANDcc)         | And (and modify condition codes)                             |

| ANDN (ANDNcc)       | And not (and modify condition codes)                         |

| ARRAY{8,16,32}      | 3-D address to blocked byte address conversion               |

| Bicc                | Branch on integer condition codes                            |

| BMASK               | Writes the GSR.mask field                                    |

| BPcc                | Branch on integer condition codes with prediction            |

| BPr                 | Branch on contents of integer register with prediction       |

| BSHUFFLE            | Permutes bytes as specified by the GSR.mask field            |

| $CALL^1$            | Call and link                                                |

| CAMELLIA_F          | Camellia F operation                                         |

| CAMELLIA_FL         | Camellia FL operation                                        |

TABLE 5-1

Complete SPARC M7 Hardware-Supported Instruction Set (2 of 6)

| Opcode              | Description                                                                    |

|---------------------|--------------------------------------------------------------------------------|

| CAMELLIA_FLI        | Camellia FLI operation                                                         |

| CASA                | Compare and swap word in alternate space                                       |

| CASXA               | Compare and swap doubleword in alternate space                                 |

| CBcond              | Fused 32 or 64 bit compare and conditional branch                              |

| CMASK{8,16,32}      | Create GSR.maskfrom SIMD operation result                                      |

| CRC32C              | CRC32C polynomial instruction                                                  |

| DES_IP              | DES initial permutation                                                        |

| DES_IIP             | DES inverse initial permutation                                                |

| DES_KEXPAND         | DES key expansion                                                              |

| DES_ROUND           | DES round                                                                      |

| DONE                | Return from trap                                                               |

| EDGE{8,16,32}{L}{N} | Edge boundary processing {little-endian} {non-condition-code altering}         |

| FABS(s,d)           | Floating-point absolute value                                                  |

| FADD(s,d)           | Floating-point add                                                             |

| FALIGNDATAg         | Perform data alignment for misaligned data                                     |

| FALIGNDATAi         | Perform data alignment for misaligned data using integer register              |

| FANDNOT1{s,d}       | Negated src1 and src2                                                          |

| FANDNOT2{s,d}       | Src1 and negated src2                                                          |

| FAND{s,d}           | Logical <b>and</b>                                                             |

| FBfcc               | Branch on floating-point condition codes                                       |

| FBPfcc              | Branch on floating-point condition codes with prediction                       |

| FCHKSM16            | 16-bit partitioned checksum                                                    |

| FCMP(s,d)           | Floating-point compare                                                         |

| FCMPE(s,d)          | Floating-point compare (exception if unordered)                                |

| FDIV(s,d)           | Floating-point divide                                                          |

| FEXPAND             | Four 8-bit to 16-bit expand                                                    |

| FHADD{s,d}          | Floating-point add and halve                                                   |

| FHSUB{s,d}          | Floating-point subtract and halve                                              |

| FiTO(s,d)           | Convert integer to floating-point                                              |

| FLCMP{s,d}          | Lexicographic compare                                                          |

| FLUSH               | Flush instruction memory                                                       |

| FLUSHW              | Flush register windows                                                         |

| FMADD{s,d}          | Floating-point multiply-add single/double (fused)                              |

| FMEAN16             | 16-bit partitioned average                                                     |

| FMOV(s,d)           | Floating-point move                                                            |

| FMOV(s,d)cc         | Move floating-point register if condition is satisfied                         |

| FMOV(s,d)R          | Move floating-point register if integer register contents satisfy condition    |

| FMSUB{s,d}          | Floating-point multiply-subtract single/double (fused)                         |

| FMUL(s,d)           | Floating-point multiply                                                        |

| FMUL8SUx16          | Signed upper 8- x 16-bit partitioned product of corresponding components       |

| FMUL8ULx16          | Unsigned lower 8- x 16-bit partitioned product of corresponding components     |

| FMUL8x16            | 8- x 16-bit partitioned product of corresponding components                    |

| FMUL8x16AL          | Signed lower 8- x 16-bit lower α partitioned product of four components        |

| FMUL8x16AU          | Signed upper 8- x 16-bit lower α partitioned product of four components        |

| FMULD8SUx16         | Signed upper 8- x 16-bit multiply → 32-bit partitioned product of components   |

| FMULD8ULx16         | Unsigned lower 8- x 16-bit multiply → 32-bit partitioned product of components |

|                     | 2-2-6-22 2000 0 120 200 Manapi, 02 200 paradioned product of components        |

TABLE 5-1

Complete SPARC M7 Hardware-Supported Instruction Set (3 of 6)

| Opcode                       | Description                                                                                 |

|------------------------------|---------------------------------------------------------------------------------------------|

| FNAND(s)                     | Logical nand (single precision)                                                             |

| FNEG(s,d)                    | Floating-point negate                                                                       |

| FNHADD{s,d}                  | Floating-point add and halve, then negate                                                   |

| FNMADD{s,d}                  | Floating-point multiply-add and negate                                                      |

| FNMSUB{s,d}                  | Floating-point negative multiply-subtract single/double (fused)                             |

| FNMUL{s,d}                   | Floating-point multiply and negate                                                          |

| FNOR{s,d}                    | Logical nor                                                                                 |

| FNOT1{s,d}                   | Negate (1's complement) src1                                                                |

| FNOT2{s,d}                   | Negate (1's complement) src2                                                                |

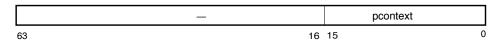

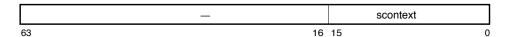

| FNsMULd                      | Floating-point multiply and negate                                                          |