OpenSPARC T1

OpenSPARC T1 is the open source version of the UltraSPARC T1 processor, a multi-core, 64-bit multiprocessor. The UltraSPARC T1 processor with CoolThreads technology was the highest-throughput and most eco-responsible processor ever created when it became available in the UltraSPARC T1 system. It was a breakthrough discovery for reducing data center energy consumption, while dramatically increasing throughput. Its 32 simultaneous processing threads, drawing about as much power as a light bulb, gave customers the best performance per watt of any processor available.

OpenSPARC T1 source components are covered under multiple open source licenses. The majority of OpenSPARC T1 source code is released under the GNU General Public License. GNU General Public License Source based on existing open source projects will continue to be available under their current licenses. Binary programs are released under a binary Software License Agreement.

OpenSPARC T1 Documents and Specifications

- OpenSPARC T1 Micro Architecture Specification

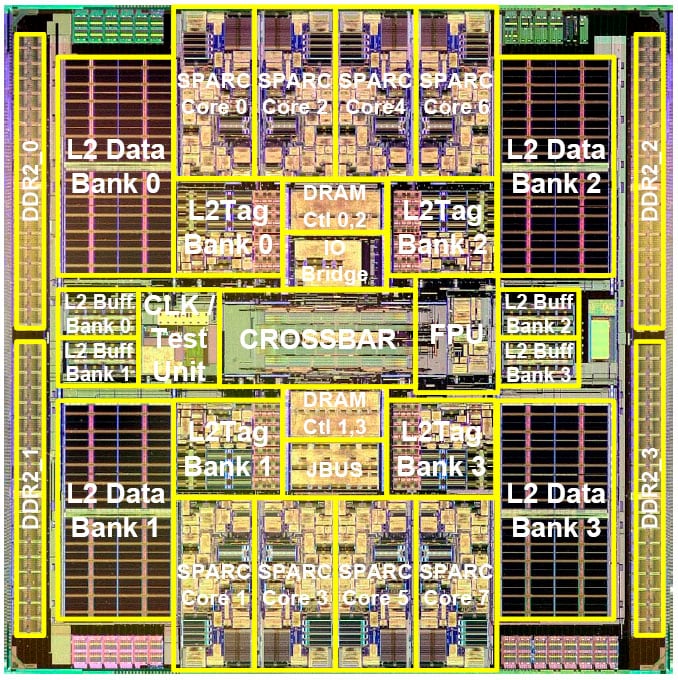

The OpenSPARC T1 Micro architecture Specification includes detailed functional descriptions of the OpenSPARC T1 Processor components. It describes the architecture of each component of the OpenSPARC T1 processor, including detailed block diagrams and signal list for each component.

- UltraSPARC Architecture 2005 Specification (Privileged Edition)

UltraSPARC Architecture 2005 Specification (Hyperprivileged Edition)

The UltraSPARC Architecture 2005 is a complete specification of the instruction set architecture (ISA) common to Sun Microsystem's 64-bit SPARC implementations (beginning with UltraSPARC T1 in 2005). UltraSPARC Architecture 2005 complies with SPARC V9 Level 1, with many more details, plus includes numerous Sun extensions common to all UltraSPARC processors. Information in this (and the following) documents can help with Operating Systems ports (including Linux).

The Privileged edition of this document (554 pages) describes the full Nonprivileged (application software) and Privileged (operating system software) levels of the architecture. Download it if you are writing application software, writing a code generator, or writing/porting operating system software to run on top of existing Hypervisor firmware (such as on a SunFire T1000 or T2000 system).

The Hyperprivileged edition of this document (678 pages) describes the Nonprivileged, Privileged, and Hyperprivileged (hypervisor/virtual machine firmware) levels of the architecture. Download it if you are writing hyperprivileged firmware ("Hypervisor" code) or designing your own processor based on OpenSPARC.

- UltraSPARC T1 supplement to UltraSPARC Architecture 2005 Specification (Privileged)

UltraSPARC T1 supplement to UltraSPARC Architecture 2005 Specification (Hyperprivileged)

This document contains information about processor-specific aspects of the architecture and programming of the UltraSPARC T1 processor. It is intended to supplement the UltraSPARC Architecture 2005 Specification with processor-specific information.

Follow the guidelines mentioned above to select whether you should download the Privileged edition (~140 pages) or Hyperprivileged edition (~360 pages) of this document.

- OpenSPARC Hypervisor Documentation

Sun's UltraSPARC T1 processor has been designed to incorporate hypervisor technology in order to present a virtualized machine environment to any guest operating system running upon it. The resulting software model for a guest operating system is referred to as the "sun4v" architecture. This virtual machine environment is implemented with a thin layer of firmware software (the "UltraSPARC Hypervisor") coupled with hardware extensions providing protection. The UltraSPARC Hypervisor not only provides system services required by the operating system, but it also enables the separation of platform resources into self-contained partitions (logical domains) each capable of supporting an independent operating system image.

Download Instructions

Downloads are available for OpenSPARC T1 processor for Chip Design and Verification and/or T1 Architecture and Performance Modeling.

- Step 1: Download one or both of the following files and then use bunzip2 command to create OpenSPARCT1.x.x.tar file. e.g. bunzip2 OpenSPARCT1.1.0.tar.bz2

OpenSPARC T1 Chip Design and Verification download

OpenSPARCT1.1.7.tar.bz2 (bzip2 compression, 255,790,781 bytes)

OpenSPARC T1 Architecture and Performance Modeling download

OpenSPARCT1_Arch.1.5.tar.bz2 (bzip2 compression, 198,858,700 bytes)

- Step 2:

Use the following command to extract files from tar file : tar xvf OpenSPARCT1.x.x.tar

- Step 3:

For the Chip Design and Verification download, please follow the instructions in the README file in the download to run simulations or synthesis. Also refer to Design/Verification Users Guide document included in the download.

For the Architecture and Performance Modeling download, please follow the instructions in the README file in the download to setup and run SAM.

OpenSPARC T1 Processor for Chip Design and Verification

OpenSPARC T1 chip source code is for hardware engineering community with experience in chip design and verification. It includes:

- Verilog RTL for OpenSPARC T1 design

- Verification environment for OpenSPARC T1

- Diagnostics tests for OpenSPARC T1

- Scripts and Sun internal tools needed to simulate the design and to do synthesis of the design

- Open source tools needed to simulate the design

- Scripts and documentation to help with FPGA implementation of parts of OpenSPARC T1 design including SPARC core, Floating point Unit, Cross-bar

System Requirements:

- SPARC CPU based system with Solaris 9 or Solaris 10 Operating System

- x86 CPU based system with Solaris 10/x86 or Red Hat Enterprise Linux 3/x86 Operating System

- C/C++ Compiler, if you don't have it download Solaris Studio 12.

Commercial EDA tools Requirements:

- Verilog Simulator : Synopsys VCS® or Cadence NC-Verilog®

- Synthesis : Synopsys Design Compiler® or Synplicity Synplify Pro®

OpenSPARC T1 Processor for Architecture and Performance Modeling Tools

SAM (SPARC Architectural Model) is a full system simulator that is able to boot Hypervisor, OBP(Open Boot PROM) and Solaris and run applications. It loads SAS (SPARC Architecture Simulator) as the OpenSPARC T1 simulator. So any modifications made in SAS get automatically reflected in SAM. SAM is useful for software bring up work -- for instance to debug Hypervisor/OBP/Solaris on a modified CPU implementation. SAM is also useful for performance analysis, both to generate traces and to connect with a performance model to perform execution driven simulation. SAM loads device models as dynamically linked libraries, and is useful for device driver development, and device rtl verification.

Legion is a fast instruction accurate simulator which provides a rapid means of developing and testing software functionality in the absence of actual hardware. Legion provides the fastest simulation environment for developing and testing SPARC Software. Firmware and Software developers will be the primary users of Legion simulation environment for the OpenSPARC T1.

This download area is for software engineers and architects, it includes

- SAM - SPARC Architecture Model (including source code)

- Legion - Fast instruction accurate simulator for software developers (including source code)

- SAM/Legion enhancements to copy files to/from simulated disk

- SAS - Instruction accurate SPARC Architecture Simulator (including source code)

- OBP - Open Boot PROM source code

- Hypervisor source code

- Solaris Images for simulation

- RST Trace Tool - RST is a trace format for SPARC instruction-level traces. The RST Tools package consists of the trace format definition, a trace reader/writer library, and a trace viewer program. Also included is a sample trace from a 32-strand application.

System Requirements:

- SPARC CPU based system with Solaris 9 or Solaris 10 Operating System

-

C/C++ Compiler, if you don't have it download Sun Studio 12.

OpenSolaris Boot

Here is the ACE file required to boot OpenSPARC on the Xilinx FPGA board and a Quick Start guide. These are included in the download but are listed here so you don't need to download the whole tarball.